# Lecture Notes in Computer Science

3553

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Timo D. Hämäläinen Andy D. Pimentel Jarmo Takala Stamatis Vassiliadis (Eds.)

# Embedded Computer Systems: Architectures, Modeling, and Simulation

5th International Workshop, SAMOS 2005 Samos, Greece, July 18-20, 2005 Proceedings

#### Volume Editors

Timo D. Hämäläinen Jarmo Takala Tampere University of Technology Institute of Digital and Computer Systems Korkeakoulunkatu 1, 33720 Tampere, Finland E-mail:{timo.d.hamalainen/jarmo.takala}@tut.fi

Andy D. Pimentel

University of Amsterdam

Department of Computer Science

Kruislaan 403, 1098 SJ Amsterdam, The Netherlands

E-mail: andy@science.uva.nl

Stamatis Vassiliadis

T.U. Delft, Computer Engineering

Mekelweg 4, 2628 CD Delft, The Netherlands

E-mail: s.vassiliadis@ewi.tudelft.nl

Library of Congress Control Number: 2005928160

CR Subject Classification (1998): C, B

ISSN 0302-9743

ISBN-10 3-540-26969-X Springer Berlin Heidelberg New York ISBN-13 978-3-540-26969-4 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11512622 06/3142 5 4 3 2 1 0

### **Preface**

The SAMOS workshop is an international gathering of highly qualified researchers from academia and industry, sharing in a 3-day lively discussion on the quiet and inspiring northern mountainside of the Mediterranean island of Samos. As a tradition, the workshop features workshop presentations in the morning, while after lunch all kinds of informal discussions and nut-cracking gatherings take place. The workshop is unique in the sense that not only solved research problems are presented and discussed but also (partly) unsolved problems and in-depth topical reviews can be unleashed in the scientific arena. Consequently, the workshop provides the participants with an environment where collaboration rather than competition is fostered.

The earlier workshops, SAMOS I–IV (2001–2004), were composed only of invited presentations. Due to increasing expressions of interest in the workshop, the Program Committee of SAMOS V decided to open the workshop for all submissions. As a result the SAMOS workshop gained an immediate popularity; a total of 114 submitted papers were received for evaluation. The papers came from 24 countries and regions: Austria (1), Belgium (2), Brazil (5), Canada (4), China (12), Cyprus (2), Czech Republic (1), Finland (15), France (6), Germany (8), Greece (5), Hong Kong (2), India (2), Iran (1), Korea (24), The Netherlands (7), Pakistan (1), Poland (2), Spain (2), Sweden (2), Taiwan (1), Turkey (2), UK (2), and USA (5). We are grateful to all of the authors who submitted papers to the workshop.

All the papers went through a rigorous reviewing process and, on average, each paper received three individual reviews. Due to time constraints in the workshop program and the high quality of the submitted papers, the selection process was very competitive and many qualified papers could not be accepted. Finally, the Program Committee selected 47 papers (corresponding to 41% of the submitted papers) for the workshop and the fifth edition of the SAMOS workshop developed into a highly interesting event. The program consisted of 32 plenary presentations (28% of the submitted papers), 15 poster presentations (13% of the submitted papers), and a keynote speech by Dr. Bob Iannucci from Nokia Research Center.

A workshop like this cannot be organized without the help of many other people. Therefore we want to thank the members of the Steering and Program Committees and the external referees for their dedication and diligence in selecting the technical presentations. The investment of their time and insight is very much appreciated. We would like to express our sincere gratitude to Timo D. Hämäläinen and Heikki Orsila for preparing the workshop proceedings, Stephen Wong for a successful publicity campaign, Elena Moscu Panainte and Iosif Antochi for maintaining the Web site and paper submission system, and Lidwina Tromp for her support in organizing the workshop.

We hope that the attendees enjoyed the SAMOS V workshop in all its aspects, including many informal discussions and gatherings.

June 2005

Andy Pimentel Stamatis Vassiliadis Jarmo Takala

# **Organization**

The SAMOS V workshop took place during July 18–20, 2005 at the Research and Teaching Institute of East Aegean (INEAG) in Agios Konstantinos on the island of Samos, Greece.

### **General Chair**

Andy Pimentel University of Amsterdam, The Netherlands

### **Program Chair**

Jarmo Takala Tampere University of Technology, Finland

### **Proceedings Chair**

Timo D. Hämäläinen Tampere University of Technology, Finland

## **Publicity Chair**

Stephen Wong Delft University of Technology, The Netherlands

### **Steering Committee**

Shuvra Bhattacharyya University of Maryland, USA Ed Deprettere Leiden University, The Netherlands

Patrice Ouinton IRISA, France

Stamatis Vassiliadis Delft University of Technology, The Netherlands Jürgen Teich University of Erlangen-Nuremberg, Germany

### **Program Committee**

Koen Bertels Delft University of Technology, The Netherlands Luigi Carro Universidade Federal do Rio Grande do Sul, Brazil

Nikitas Dimopoulos University of Victoria, Canada

Pedro Diniz University of Southern California, USA

### VIII Organization

Gerhard Fettweis Technische Universität Dresden, Germany Georgi Gaydadjiev Delft University of Technology, The Netherlands

John GlossnerSandbridge Technologies, USADavid GuevorkianNokia Research Center, FinlandWayne LukImperial College London, UK

Bernard Pottier Université de Bretagne Occidentale, France

Tanguy Risset IRISA/INRIA, France

Michael Schulte University of Wisconsin-Madison, USA

Dirk Stroobandt Ghent University, Belgium

Jarmo Takala Tampere University of Technology, Finland

Serge Vernalde IMEC, Belgium

Jens Peter Wittenburg Thomson Corporate Research, Germany

### **Local Organizers**

Lidwina Tromp Delft University of Technology, The Netherlands Yiasmin Kioulafa Research and Training Institute of East Aegean, Greece

### Referees

Antochi, I. Galuzzi, C. Kuorilehto, M. Bhattacharyya, S. Gaydadjiev, G. Kuzmanov, G. Bertels, K. Gehrke, W. Langemeyer, S. Bertels, P. Glossner, J. Langerwerf, J.M. Blem, E. Guevorkian, D. Lee, D.U. Brune, T. Guzma, V. Lehtoranta, O.

Calderon, H. Han, X. Li. B. Carro, L. Hannig, F. Li. S. Chang, Z. Heikkinen, J. Luk, W. Cheung, R. Heirman, W. Mamidi, S. Christiaens, M. Martin, B. Hur, J.Y. Crisu. D. Hämäläinen, P. Matus, E. Mhamdi, L. de Langen, P. Hämäläinen, T. Devos, H. Iancu, D. Molnos, A.

Dimond, R. Jackowski, E. Moscu Panainte, E. Dimopoulos, N. Janes, D. Moudgill, M. Diniz, P. Jinturkar, S. Nacer, G. Duarte, F. Järvinen, T. Narkhede, P. Erbas, C. Kachris, C. Orsila, H. Faes, P. Kangas, T. Pieper, S. Fettweis, G. Keinert, J. Pimentel, A. Fidjeland, A. Koch, D. Polstra, S.

Gaedke, K. Kropp, H. Pottier, B.

Pourebrahimi, B.

Punkka, K.

Putzke-Röming, W.

Quinton, P.

Reuter, C.

Rissa, T.

Robelly, P.

Salmela, P.

Salminen, E.

Schulte, M.

Sedcole, P.

Senthilvelan, M. Silvén, O. Sima, M. Smailbegovic, F. Sourdis, I. Stanek, Z. Streichert, T. Stroobandt, D. Strydis, C. Takala, J. Teich, J. Tsen, C. Wang, L.-K. Vassiliadis, S. Vayá, G.P. Winter, M. Wittenburg, J. Yli-Pietilä, T. Yusuf, S. Yuwono, I.

# **Table of Contents**

# Keynote

| Platform Thinking in Embedded Systems  Bob Iannucci                                                                                                 | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Reconfigurable System Design and Implementations                                                                                                    |    |

| Interprocedural Optimization for Dynamic Hardware Configurations  Elena Moscu Panainte, Koen Bertels, Stamatis Vassiliadis                          | 2  |

| Reconfigurable Embedded Systems: An Application-Oriented Perspective on Architectures and Design Techniques                                         |    |

| M. Glesner, H. Hinkelmann, T. Hollstein, L.S. Indrusiak, T. Murgan, A.M. Obeid, M. Petrov, T. Pionteck, P. Zipf                                     | 12 |

| Reconfigurable Multiple Operation Array  Humberto Calderon, Stamatis Vassiliadis                                                                    | 22 |

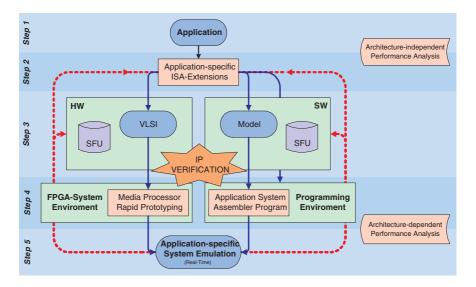

| RAPANUI: Rapid Prototyping for Media Processor Architecture Exploration  Guillermo Payá Vayá, Javier Martín Langerwerf, Peter Pirsch                | 32 |

| Data-Driven Regular Reconfigurable Arrays: Design Space Exploration and Mapping  Ricardo Ferreira, João M.P. Cardoso, Andre Toledo, Horácio C. Neto | 41 |

| Automatic FIR Filter Generation for FPGAs  Holger Ruckdeschel, Hritam Dutta, Frank Hannig, Jürgen Teich                                             | 51 |

| Two-Dimensional Fast Cosine Transform for Vector-STA Architectures  J.P. Robelly, A. Lehmann, G. Fettweis                                           | 62 |

| Configurable Computing for High-Security/High-Performance Ambient Systems                                                                           |    |

| Guy Gogniat, Wayne Burleson, Lilian Bossuet                                                                                                         | 72 |

| FPL-3E: Towards Language Support for Reconfigurable Packet Processing  Mihai Lucian Cristea, Claudiu Zissulescu, Ed Deprettere, Herbert Bos         | 82 |

# **Processor Architectures, Design and Simulation**

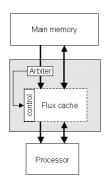

| Flux Caches: What Are They and Are They Useful?  Georgi N. Gaydadjiev, Stamatis Vassiliadis                                                     | 93  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

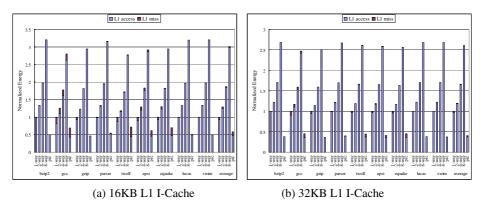

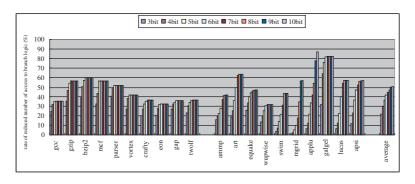

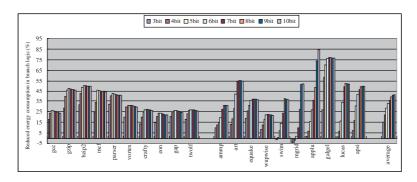

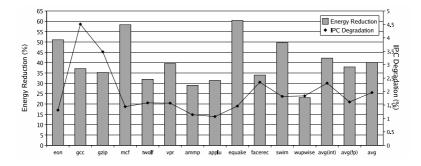

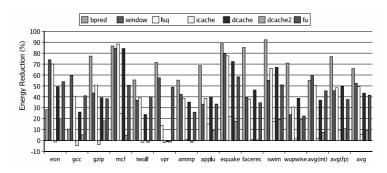

| First-Level Instruction Cache Design for Reducing Dynamic Energy<br>Consumption  Cheol Hong Kim, Sunghoon Shim, Jong Wook Kwak, Sung Woo Chung, |     |

| Chu Shik Jhon                                                                                                                                   | 103 |

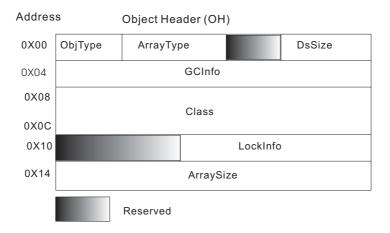

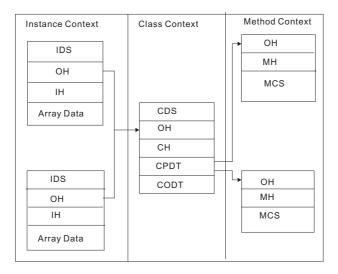

| A Novel JAVA Processor for Embedded Devices  Yiyu Tan, Chihang Yau, Kaiman Lo, Paklun Mok, Anthony S. Fong                                      | 112 |

| Formal Specification of a Protocol Processor  Tomi Westerlund, Juha Plosila                                                                     | 122 |

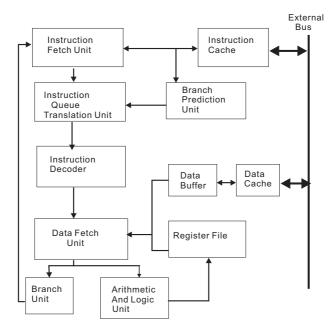

| Tuning a Protocol Processor Architecture Towards DSP Operations  Jani Paakkulainen, Seppo Virtanen, Jouni Isoaho                                | 132 |

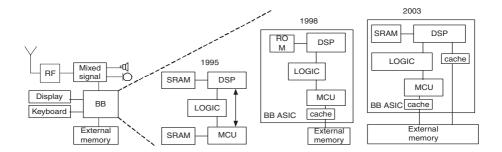

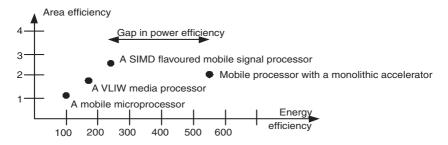

| Observations on Power-Efficiency Trends in Mobile Communication Devices Olli Silvén, Kari Jyrkkä                                                | 142 |

| CORDIC-Augmented Sandbridge Processor for Channel Equalization  Mihai Sima, John Glossner, Daniel Iancu, Hua Ye, Andrei Iancu,  A. Joseph Hoane | 152 |

| Power-Aware Branch Logic: A Hardware Based Technique for Filtering Access to Branch Logic                                                       |     |

| Sunghoon Shim, Jong Wook Kwak, Cheol Hong Kim, Sung Tae Jhang, Chu Shik Jhon                                                                    | 162 |

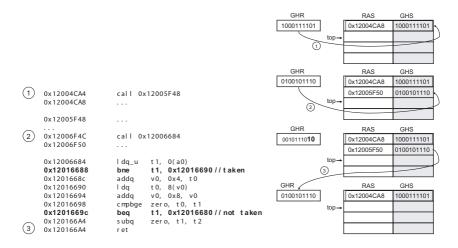

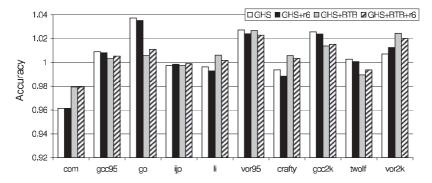

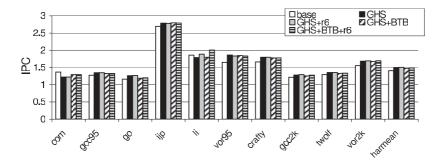

| Exploiting Intra-function Correlation with the Global History Stack  Fei Gao, Suleyman Sair                                                     | 172 |

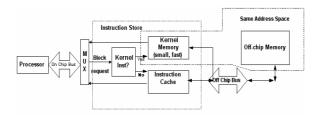

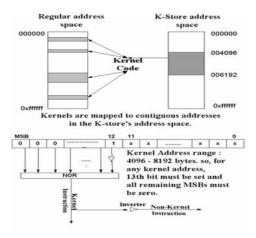

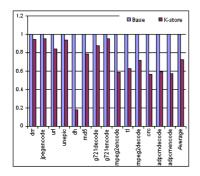

| Power Efficient Instruction Caches for Embedded Systems  Dinesh C. Suresh, Walid A. Najjar, Jun Yang                                            | 182 |

| Micro-architecture Performance Estimation by Formula  Lucanus J. Simonson, Lei He                                                               | 192 |

| Offline Phase Analysis and Optimization for Multi-configuration Processors  Frederik Vandeputte, Lieven Eeckhout, Koen De Bosschere             | 202 |

| Hardware Cost Estimation for Application-Specific Processor Design  Teemu Pitkänen, Tommi Rantanen, Andrea Cilio, Jarmo Takala                  | 212 |

A Radix-8 Multiplier Design and Its Extension for Efficient Implementation

Ville Lappalainen .....

324

David Guevorkian, Petri Liuha, Aki Launiainen, Konsta Punkka,

of Imaging Algorithms

| A Scalable Embedded JPEG2000 Architecture  Chunhui Zhang, Yun Long, Fadi Kurdahi                                                                                             | 334 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

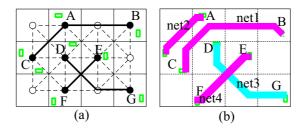

| A Routing Paradigm with Novel Resources Estimation and Routability Models for X-Architecture Based Physical Design Yu Hu, Tong Jing, Xianlong Hong, Xiaodong Hu, Guiying Yan | 344 |

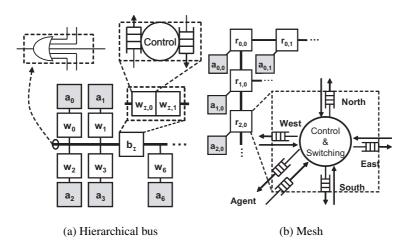

| Benchmarking Mesh and Hierarchical Bus Networks in System-on-Chip Context  Erno Salminen, Tero Kangas, Jouni Riihimäki, Vesa Lahtinen,                                       |     |

| Kimmo Kuusilinna, Timo D. Hämäläinen                                                                                                                                         | 354 |

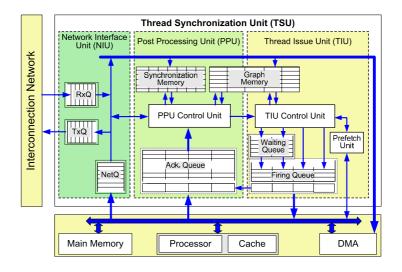

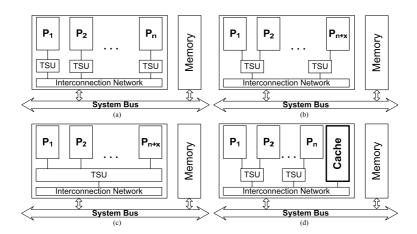

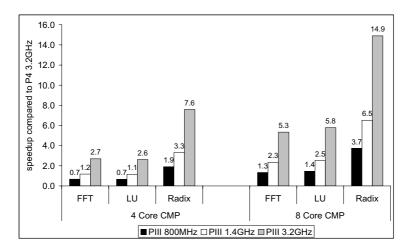

| DDM-CMP: Data-Driven Multithreading on a Chip Multiprocessor Kyriakos Stavrou, Paraskevas Evripidou, Pedro Trancoso                                                          | 364 |

| System Level Design, Modeling and Simulation                                                                                                                                 |     |

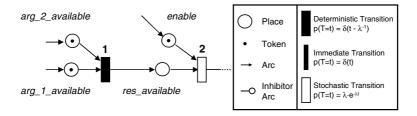

| Modeling NoC Architectures by Means of Deterministic and Stochastic Petri<br>Nets                                                                                            |     |

| H. Blume, T. von Sydow, D. Becker, T.G. Noll                                                                                                                                 | 374 |

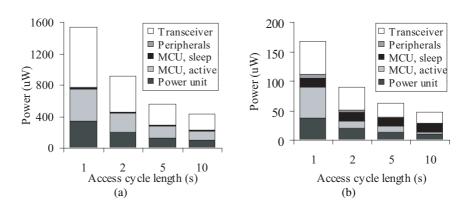

| High Abstraction Level Design and Implementation Framework for Wireless<br>Sensor Networks                                                                                   |     |

| Mauri Kuorilehto, Mikko Kohvakka, Marko Hännikäinen,<br>Timo D. Hämäläinen                                                                                                   | 384 |

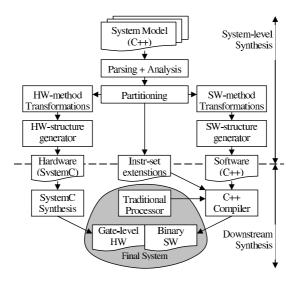

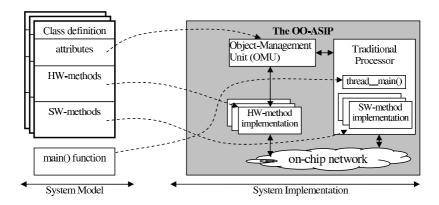

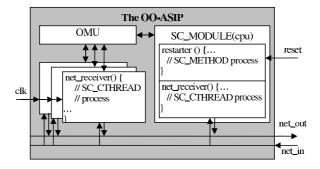

| The ODYSSEY Tool-Set for System-Level Synthesis of Object-Oriented Models                                                                                                    |     |

| Maziar Goudarzi, Shaahin Hessabi                                                                                                                                             | 394 |

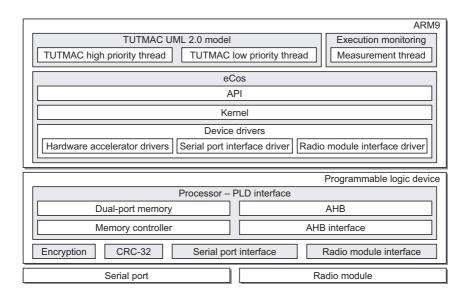

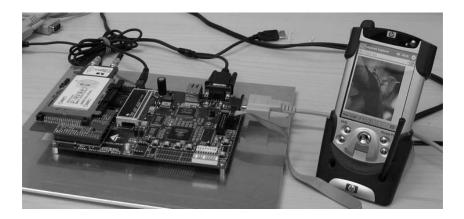

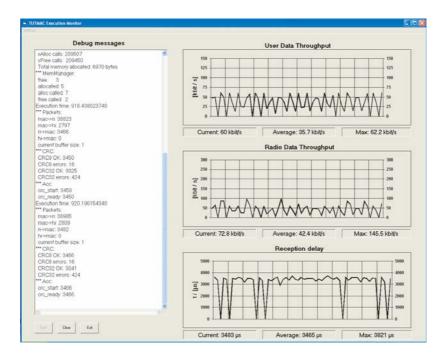

| Design and Implementation of a WLAN Terminal Using UML 2.0 Based Design Flow                                                                                                 |     |

| Petri Kukkala, Marko Hännikäinen, Timo D. Hämäläinen                                                                                                                         | 404 |

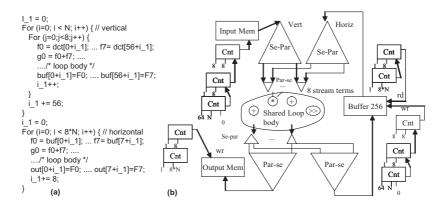

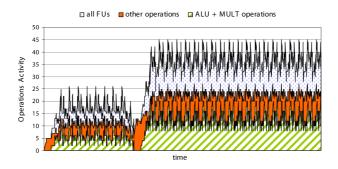

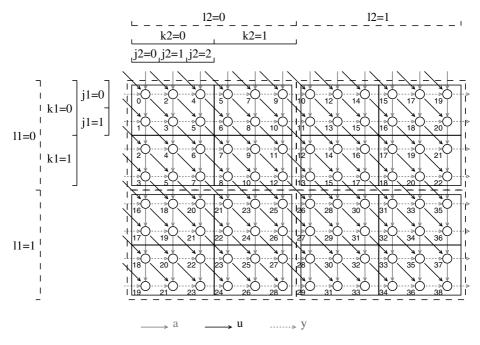

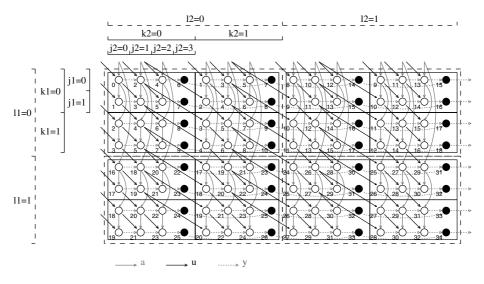

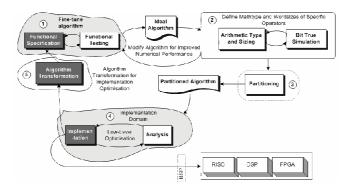

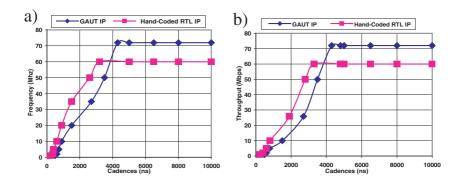

| Rapid Implementation and Optimisation of DSP Systems on SoPC<br>Heterogeneous Platforms                                                                                      |     |

| J. McAllister, R. Woods, D. Reilly, S. Fischaber, R. Hasson                                                                                                                  | 414 |

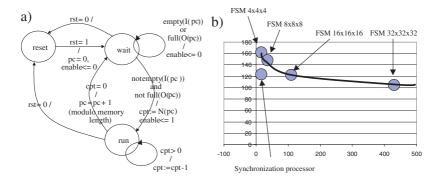

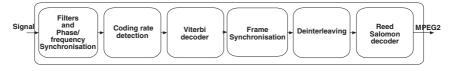

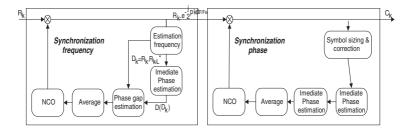

| DVB-DSNG Modem High Level Synthesis in an Optimized Latency<br>Insensitive System Context                                                                                    |     |

| P. Bomel, N. Abdelli, E. Martin, AM. Fouilliart, E. Boutillon, P. Kajfasz                                                                                                    | 424 |

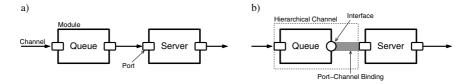

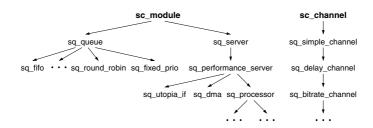

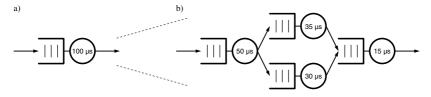

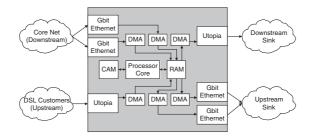

| SystemQ: A Queuing-Based Approach to Architecture Performance Evaluation with SystemC                                                                                        |     |

| Sören Sonntag, Matthias Gries, Christian Sauer                                                                                                                               | 434 |

Table of Contents

XV

# **Platform Thinking in Embedded Systems**

#### Bob Iannucci

Nokia Research Center, Itämerenkatu 11-13, 00180 Helsinki, Finland

**Abstract.** Modern embedded systems are built from microprocessors, domainspecific hardware blocks, communication means, application-specific sensor/actuators and as simple as possible user interface, which hides the embedded complexity. The design of embedded systems is typically done in an integrated way with strong dependencies between these building block elements and between different parts of the system. This talk focuses on how platform thinking and engineering can be applied to increasingly complex embedded systems and what impacts that will have on the design and architectures. Platform engineering in embedded systems may sound contradictory, but in practice will introduce modularity and stable interfaces. New system-level architectures for hardware, middleware architectures, and certifiable operating system micro-kernels are needed to raise the abstraction level and productivity of design. As an example I will go through the definitions of some modules in a mobile device and the requirements for their interfaces. I will describe the additional design steps, new formal methods and system-level tasks that are needed in the platform approach. Finally, I will review the Advanced Research and Technology for Embedded and Intelligent Systems (ARTEMIS) technology platform in EU 7th Framework Program, which is bringing together industrial and academic groups to create coherent and integrated European research in the domain of embedded systems.

# Interprocedural Optimization for Dynamic Hardware Configurations

Elena Moscu Panainte, Koen Bertels, and Stamatis Vassiliadis

Computer Engineering Lab,

Delft University of Technology, The Netherlands

{E.Panainte, K.Bertels, S.Vassiliadis}@et.tudelft.nl

**Abstract.** Little research in compiler optimizations has been undertaken to eliminate or diminish the negative influence on performance of the huge reconfiguration latency of the available FPGA platforms. In this paper, we propose an interprocedural optimization that minimizes the number of executed hardware configuration instructions taking into account constraints such as the "FPGA-area placement conflicts" between the available hardware configurations. The proposed algorithm allows the anticipation of hardware configuration instructions up to the application's main procedure. The presented results show that our optimization produces a reduction of up to 3 - 5 order of magnitude of the number of executed hardware configuration instructions.

### 1 Introduction

The combination of a general purpose processor (GPP) and a Field Programmable Gate Array (FPGA) is becoming increasingly popular (e.g. [1], [2], [3], [4], [5] and [6]). Reconfigurable computing (RC) is a new style of computer architecture which allows the designer to combine the advantages of both hardware (speed) and software (flexibility). However, an important drawback of the RC paradigm is the huge reconfiguration latency of the actual FPGA platforms. As presented in [7], the potential speedup of the kernel hardware executions can be completely wasted by the repetitive hardware configurations that produce a performance decrease of up to 2 order of magnitude.

When targeting reconfigurable architectures, the compiler should be aware of the competition for the reconfigurable hardware resources (FPGA area) between multiple hardware operations during the application execution time. A new type of conflict - called in this paper "FPGA area placement conflict" - emerges between two hardware configurations that cannot coexist together on the target FPGA.

In this paper, we propose an interprocedural optimization that anticipates hardware configuration instructions up to the application's main procedure. The optimization takes into account constraints such as the "FPGA-area placement conflicts" between the available hardware configurations. The presented results show that a reduction of up to 3 - 5 order of magnitude of the number of executed hardware configuration instructions is expected for MPEG2 and M-JPEG multimedia applications.

This paper is organized as follows. Section 2 presents background information and related work for compiler optimizations targeting dynamic hardware configuration in-

structions, followed by a motivational example in Section 3. The proposed interprocedural optimization algorithm is introduced in Section 4. Experimental results for two multimedia applications are provided in Section 5, and Section 6 presents the concluding remarks.

### 2 Background and Related Work

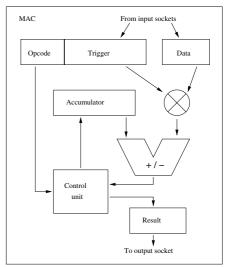

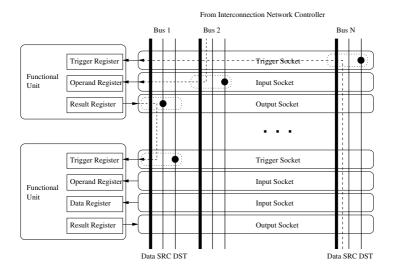

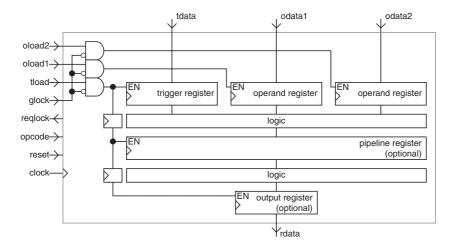

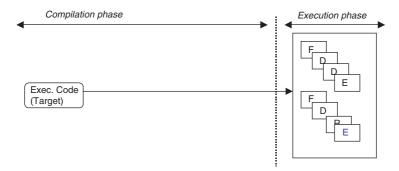

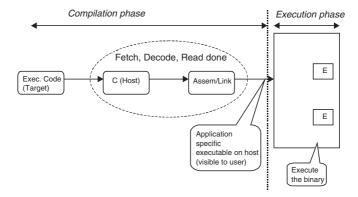

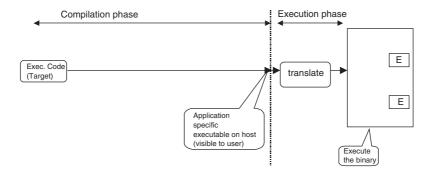

In this paper, we assume the Molen programming paradigm ([8], [9])which is a sequential consistency paradigm for programming Field-Programmable Custom Computing Machines(FCCMs) possibly including a general purpose computational engine(s). The paradigm allows for parallel and concurrent hardware execution and is intended (currently) for single program execution. It requires only a one time architectural extension of few instructions to provide a large user reconfigurable operation space. The added instructions include **SET** < *address* > for reconfigurable hardware configuration and **EXECUTE** < *address* > for controlling the executions of the operations on the reconfigurable hardware. In addition, two MOVE instructions for passing values to and from the GPP register file and the reconfigurable hardware are required.

In order to achieve significant performance improvement for real applications, more operations are usually executed on the reconfigurable hardware. As the available area of the reconfigurable platforms is limited, the coexistence of all hardware configurations on the FPGA for all application execution time may be restricted, resulting in "FPGA-area placement conflicts". Two hardware operations have an "FPGA-area placement conflict" (or just conflict in the rest of the paper) if i) their combined reconfigurable hardware area is larger than the total FPGA area or ii) the intersection of their hardware areas is not empty.

Several approaches have been proposed for reducing the impact of the reconfiguration latency on performance. A compiler approach that considers the restricted case of two consecutive and non-conflicting hardware operations is presented in [10]. In this approach, the hardware execution of the first operation is scheduled in parallel with the hardware configuration of the second operation. Our approach is more general as it performs scheduling for any number of hardware operations at procedural level and not only for two consecutive hardware operations. The performance gain produced by our scheduling algorithm results from reducing the number of performed hardware configurations. In [11], the reconfiguration overhead is reduced by using manual interprocedural optimizations such as localizing memory accesses, partial hardware reuse and pipeling. Our approach is different as the optimization is automatically applied in the compilation phase and it minimizes the number of performed hardware configurations without specific information about the target FPGA and hardware operations. The instruction scheduling approach presented in [12] uses data-flow analyses and profile information for reducing the number of executed hardware configurations. In this paper, we extend this approach at interprocedural level, taking into account all procedures of the target applications. As a consequence, the impact of the proposed optimization is significantly increased as presented in Section 5.

### 3 Motivation and Contribution

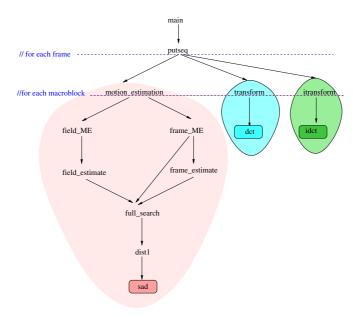

In order to illustrate the goals and the main features of the proposed interprocedural optimization, we present in Fig. 1 a motivational real example. The presented subgraph is included in the call graph of the MPEG2 encoder multimedia benchmark where an edge  $\langle p_i, p_j \rangle$  represents a call from procedure  $p_i$  to procedure  $p_j$ . We consider that the procedures SAD, DCT and IDCT are executed on the reconfigurable hardware and that initially the hardware configuration (a SET instruction) is performed before each hardware execution (an EXEC instruction). One first observation is that the configuration for the SAD operation can be safely anticipated in the **motion\_estimation** procedure. This anticipation will significantly reduce the number of performed hardware configurations as it will not be performed for each macroblock but only for each frame of the input sequence. This observation also holds for the DCT configuration in transform and the IDCT configuration in itransform. Moreover, the SAD configuration from motion\_estimation can be moved upwards in the putseq procedure, immediately preceding the call site of motion\_estimation in putseq. Additionally, it can be noticed that the propagation of the SAD configuration from **putseq** to the **main** procedure depends on the FPGA area allocation for SAD, DCT and IDCT. When the SAD operation does not have any FPGA-area placement conflict with the other two hardware operations DCT and IDCT, its configuration can be safely performed only once, at the entry point in the main procedure.

The contribution of this paper includes the following. The optimization proposed in this paper allows to anticipate the hardware configurations at interprocedural level, while prior work was limited to optimizations at procedural level (intraprocedural).

Fig. 1. Motivational example for MPEG2 encoder

Secondly, although the interprocedural optimizations are considered to provide little benefit and significantly increase the compiler complexity, we show that our optimization significantly reduces the number of hardware configurations (a major drawback of the current FPGAs).

# 4 Interprocedural Optimization for Dynamic Hardware Configurations

The main goal of the proposed interprocedural optimization presented in this section is to anticipate the dynamic hardware configuration instructions taking into account the hardware conflicts between the available hardware operations. As such hardware configuration does not cause an exception, a speculative algorithm is used for anticipating the hardware configuration instructions. The interprocedural optimization consists of three steps. In the first step, the program's call graph is constructed based on an interprocedural control-flow analysis. Next, the set of live hardware configurations for each procedure is determined using an interprocedural data-flow analysis. Finally, the hardware configuration instructions are anticipated in the call graph taking into account the available conflicting operations.

# 4.1 Step 1: Interprocedural Control-Flow Analysis for Dynamic Hardware Configurations

Starting point of the proposed optimization is the construction of the program's call graph. Given a program P consisting of a set of procedures  $\langle p_1, p_2, ..., p_n \rangle$ , the program's call graph of P is the graph  $G = \langle N, E, r \rangle$  with the node set  $N = \{p_1, p_2, ..., p_n\}$ , the set  $E \subseteq N \times N$ , where  $\langle p_i, p_j \rangle \in E$  denotes a call site in  $p_i$  from which  $p_j$  is called, and the distinguished entry node  $r \in N$  representing the main entry procedure of the program . An example of a real call (sub)graph is presented in Fig. 1.

The construction of the call graph for a program written in C is straightforward as there are no higher-order procedures in the C programming language. For this purpose, we used the *sbrowser\_cg* library included in the *suifbrowser* package available in the SUIF environment. The constructed call graph is the input of the optimization algorithm presented in Table 1. As explained in the next subsection, the constructed graph is required to be a DAG (Directed Acyclic Graph) (see Table 1, step 1).

# **4.2** Step 2: Interprocedural Data-Flow Analysis for Dynamic Hardware Configurations

The goal of the interprocedural data-flow analysis is to determine what hardware operation can modify the FPGA configuration as a side effect of a procedure call. We define LRMOD(p) (Local Reconfigurable hardware MODification) as the set of hardware operations associated with a procedure p. In order to simplify this discussion, we assume that there is at most one hardware operation that can be associated with a procedure. More specifically,  $op_1 \in LRMOD(p)$  if there is a pragma annotation that indicates that procedure p is executed on the reconfigurable hardware and its associated hardware operation is named  $op_1$ . RMOD(p), Reconfigurable hardware MODification, represents

Table 1. The interprocedural optimization algorithm for hardware configuration instructions

```

Interprocedural Optimization Algorithm

INPUT: Call graph G = \langle N, S, r \rangle, hardware conflicts f : HWxHW - \rangle \{0, 1\}

OUTPUT: Insertion edges L

1. //Verify assumptions for G

check if G is DAG

2. //RMOD computation

traverse G in reverse topological order

compute for each procedure p

RMOD(p) = LRMOD(p) \bigcup

RMOD(s)

s \in Succ(p)

//Compute CF

for each procedure p

CF(p) = \{op_1 \in RMOD(p) | \exists op_2 \in RMOD(p), op_1 \leftrightarrow op_2\}

3. //Compute the insertion edges

L = \emptyset

for each edge \langle p_i, p_i \rangle

for each op \in [RMOD(p_i) - CF(p_i)] \cap CF(p_i)

L = L \cup \langle p_i, p_j, op \rangle

for each op \in [RMOD(r) - CF(r)]

L = L \cup \langle r, r, op \rangle

```

the set of all hardware operations that may be executed by an invocation of procedure p and it can be computed using the following data-flow equation:

$$RMOD(p) = LRMOD(p) \bigcup_{s \in Succ(p)} RMOD(s)$$

(1)

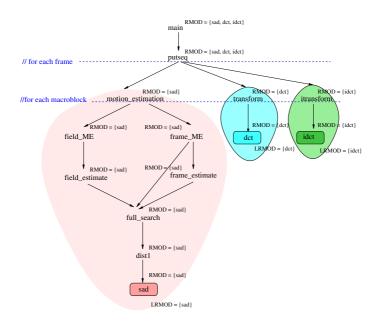

A hardware operation op may be performed by calling procedure p if op is associated with procedure p (i.e.  $op \in LRMOD(p)$ ) or if it can be performed by a procedure that is called from procedure p. For an efficient computation, the RMOD values should be computed in reverse topological order (i.e. reverse invocation order) when the call graph does not contain cycles (see step 2 from Table 1). The RMOD values for the example presented in Fig. 1 are shown in Fig. 2. For the basic blocks where LRMOD values are missing, they are implicitly assumed as  $\emptyset$ . We notice that by calling putseq procedures, all three hardware operations sad,dct and idct may be executed on the reconfigurable hardware.

Due to the increasing complexity of the interprocedural data-flow analysis, this step is performed only when the call graph G satisfies the following criteria. We assume that there are no *indirect procedure calls* (using pointer to functions). These limitations can be eliminated by considering all candidate set of functions that have the same prototype. Another limitation concerns the data-flow equations for procedures with recursive procedure calls (when the call graph contains cycles). In this case, the strongly connected

Fig. 2. Interprocedural data-flow analysis for MPEG2 encoder

components (scc) should be computed and the data-flow equations should be collapsed for each scc into a single equation. The proposed optimization is applied only when the call graph is a DAG.

# 4.3 Step 3: Interprocedural Scheduling for Dynamic Hardware Configuration Instructions

In this step, the hardware configuration instructions are anticipated in the call graph taking into account the possible hardware conflicts discovered in the previous step. In the first phase, the set of conflicting operations CF(p) is computed for each procedure included in the call graph based on the RMOD values as follows:

$$CF(p) = \{op_1 \in RMOD(p) | \exists op_2 \in RMOD(p), op_1 \leftrightarrow op_2\}$$

(2)

Next, for each edge of the call graph  $< p_i, p_j >$ , if there is an hardware operation op which does not have conflicts in  $p_j$  ( $op \not\in CF(p_j)$ ) but it has conflicts in the calling function  $p_i$  ( $op \in CF(p_i)$ ), then a SET op instruction is inserted at all call sites of  $p_j$  from  $p_i$ . Finally, for all non-conflicting operations of the entry node of the call graph G (i.e. RMOD(r) - CF(r)), the corresponding SET instructions are inserted at the beginning of the r procedure (see step 3 from Table 1).

The CF values for the example presented in Fig. 1 are shown in Fig. 3, for the case where all considered hardware operations conflict with each other. For the basic blocks where CF values are missing they are implicitly assumed as  $\emptyset$ . It can be noticed that the hardware configuration instructions cannot simultaneously propagate upwards of *putseq* procedure due to the considered hardware conflicts.

Fig. 3. Interprocedural optimization for MPEG2 encoder

### 5 Results

In order to present the results of our algorithm with respect to the number of performed hardware configurations, we first describe the experimental setup, including the target architecture and applications. Next, we concentrate on the impact of the optimization on the number of hardware configurations. Finally we present several important observations about the presented results and possible improvements of the optimization algorithm.

### 5.1 Experimental Setup

The application domain of these experiments is video data compressing. We consider two real-life applications namely Motion JPEG (M-JPEG) encoder which compresses sequences of video frames applying JPEG compression for each frame and the MPEG2 encoder multimedia benchmark. The input test sequence for M-JPEG contains 30 color frames from "tennis" in YUV format with a resolution of 256x256 pixels. For MPEG2 encoder, we used the standard test frames included in the benchmark. The operations considered for execution on the FPGA for the M-JPEG applications are DCT (2-D Discrete Cosine Transform), Quantization and VLC (Variable Length Coding), while for MPEG2 the candidates are SAD (Sum of Absolute-Difference), DCT and IDCT (inverse DCT).

The described optimization algorithm has been implemented in the Molen compiler, more specifically in the SUIF compiler frontend. We used the *link\_suif* pass that combines all input SUIF files, making their global symbol tables consistent and the *sbrowser\_cg* library included in the *suifbrowser* package available in the SUIF environ-

ment for the construction of the interprocedural call graph. The call graph for the M-JPEG encoder includes 47 nodes (i.e. the applications contains 47 procedures), while the call graph for MPEG2 encoder (a subgraph is presented in Fig. 1) has 111 nodes.

### 5.2 Interprocedural Optimization Results

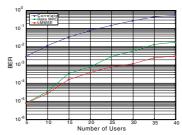

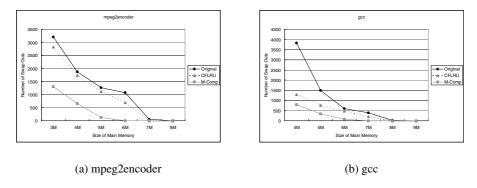

The aim of the proposed optimization is to significantly reduce the number of the executed SET instructions for each hardware operation. In the results presented in the rest of this section, we compare the number of executed hardware configurations with and without our optimization (denoted as SET\_OPT and respectively NO\_SET\_OP cases).

M-JPEG Encoder Results. Table 2 shows the number of hardware configurations required in the M-JPEG encoder multimedia application for the SET\_OPT (columns 3-7) and NO\_SET\_OPT (column 2) cases. When measuring the effects of the proposed optimization (Table 2, columns 3-7), we consider different possible conflicts between DCT, Quant and VLC; in the best case there is no conflict (column 3), while in the worst case all hardware operations are in conflict with each other (column 7). The first observation is that, for the *no conflict* case, our optimization algorithm eliminates all hardware configurations and introduces at the application entry point only one hardware configuration for each hardware operation; thus, all the hardware configurations but one from the initial application (Table 2, column 2) are redundant. A second observation is that our optimization reduces the number of DCT hardware configurations with at least 75 % for all conflict cases. Finally, we notice that even for the worst case (Table 2, columns 7), the proposed optimization reduces the number of executed SET instructions for DCT configuration by 4x. This reduction is due to the anticipation of DCT hardware configuration at the macroblock level, while the configurations for Quant and VLC are already performed at this level and cannot be anticipated upwards due to the hardware conflicts.

**MPEG2 Encoder Results.** The number of hardware configurations for the considered functions in the MPEG2 encoder benchmark is presented in Table 5.2. One important observation is the 3-5 order of magnitude decrease of the number of hardware configurations produced by our optimization algorithm for all conflict cases. The main cause of this decrease is the particular features of the MPEG2 algorithm where the SAD, DCT

**Table 2.** The impact of the interprocedural optimization on the number of required hardware configurations in M-JPEG encoder

|       | Initial  | With interprocedural SET optimization |           |          |           |               |

|-------|----------|---------------------------------------|-----------|----------|-----------|---------------|

| HW op | [# SETs] | No                                    | DCT Quant | DCT VLC  | Quant VLC | DCT Quant VLC |

|       |          | conflict                              | conflict  | conflict | conflict  | conflict      |

| DCT   | 61440    | 1                                     | 15360     | 15360    | 1         | 15360         |

| Quant | 15360    | 1                                     | 15360     | 1        | 15360     | 15360         |

| VLC   | 15360    | 1                                     | 1         | 15360    | 15360     | 15360         |

|       | Initial  |          | With interprocedural SET optimization |          |          |              |

|-------|----------|----------|---------------------------------------|----------|----------|--------------|

| HW op | [# SETs] | No       | SAD DCT                               | SAD IDCT | DCT IDCT | SAD DCT IDCT |

|       |          | conflict | conflict                              | conflict | conflict | conflict     |

| SAD   | 117084   | 1        | 3                                     | 3        | 1        | 3            |

| DCT   | 1152     | 1        | 3                                     | 1        | 3        | 3            |

| IDCT  | 1152     | 1        | 1                                     | 3        | 3        | 3            |

**Table 3.** The impact of the interprocedural optimization on the number of required hardware configurations in MPEG2 encoder

and IDCT hardware configurations can be anticipated out to the frame level rather than macroblock level (see Fig. 3). In consequence, due to our optimization algorithm, the hardware configuration is transformed from a major bottleneck in a negligible factor on performance.

In order to conclude this section, four points should be noticed regarding the presented results and optimization. Firstly, the reduction of the number of hardware configurations depends on the characteristics of the target applications. As previously presented, the impact of our optimizations for MPEG2 encoder is substantial, while for other applications (e.g. M-JPEG) it depends on the possible hardware conflicts between operations. Second, it should be mentioned that this optimization can also increase the number of hardware configurations, e.g. when the considered procedure associated to the hardware operations have multiple call sites and conflicting operations. Flow-sensitive data-flow analysis and profile information can be used to prevent this situation. Nevertheless, taking into account that the hardware configuration can be performed in parallel with the execution of other instructions on the GPP, the reconfiguration latency may be (partially) hidden. The final major point is that a significant reduction of the number of executed hardware configurations is directly reflected in a significant reduction in power consumption, as the FPGA reconfigurations is a main source of power consumption.

#### 6 Conclusions

In this paper, we have proposed an interprocedural optimization algorithm for hardware configuration instructions. This algorithm takes into account specific features of the target applications and of the reconfigurable hardware such as the "FPGA area placement conflicts". It allows the anticipation of hardware configuration instructions up to the application's main procedure. The presented results show that our optimization produces a reduction of up to 3 - 5 order of magnitude of the number of executed hardware configuration instructions for the MPEG2 and M-JPEG multimedia benchmarks.

Future research will focus on compiler optimizations to allow for concurrent execution. We also intend to extend the compiler to provide information for an efficient FPGA area allocation of the different hardware operations in order to eliminate the FPGA-area placement conflicts.

### References

- Campi, F., Cappelli, A., Guerrieri, R., Lodi, A., Toma, M., Rosa, A.L., Lavagno, L., Passerone, C.: A reconfigurable processor architecture and software development environment for embedded systems. In: Proceedings of Parallel and Distributed Processing Symposium, Nice, France (2003) 171–178

- Sima, M., Vassiliadis, S., S.Cotofana, van Eijndhoven, J., Vissers, K.: Field-Programmable Custom Computing Machines - A Taxonomy. In: 12th International Conference on Field Programmable Logic and Applications (FPL). Volume 2438., Montpellier, France, Springer-Verlag Lecture Notes in Computer Science (LNCS) (2002) 79–88

- Becker, J.: Configurable Systems-on-Chip: Commercial and Academic Approaches. In: Proc. of 9th IEEE Int. Conf. on Electronic Circuits and Systems - ICECS 2002, Dubrovnik, Croatia (2002) 809–812

- Gokhale, M.B., Stone, J.M.: Napa C: Compiling for a Hybrid RISC/FPGA Architecture. In: Proceedings of FCCM'98, Napa Valley, CA (1998) 126–137

- Rosa, A.L., Lavagno, L., Passerone, C.: Hardware/Software Design Space Exploration for a Reconfigurable Processor. In: Proc. of DATE 2003, Munich, Germany (2003) 570–575

- 6. Ye, Z.A., Shenoy, N., Banerjee, P.: A C Compiler for a Processor with a Reconfigurable Functional Unit. In: ACM/SIGDA Symposium on FPGAs, Monterey, California, USA (2000) 95–100

- Moscu Panainte, E., Bertels, K., Vassiliadis, S.: Dynamic hardware reconfigurations: Performance impact on mpeg2. In: Proceedings of SAMOS. Volume 3133., Samos, Greece, Springer-Verlag Lecture Notes in Computer Science (LNCS) (2004) 284–292

- 8. Vassiliadis, S., Gaydadjiev, G., Bertels, K., Moscu Panainte, E.: The Molen Programming Paradigm. In: Proceedings of the Third International Workshop on Systems, Architectures, Modeling, and Simulation, Samos, Greece (2003) 1–7

- Vassiliadis, S., Wong, S., Gaydadjiev, G.N., Bertels, K., Kuzmanov, G., Moscu Panainte, E.: The Molen Polymorphic Processor. IEEE Transactions on Computers 53(11) (2004) 1363–1375

- Tang, X., Aalsma, M., Jou, R.: A Compiler Directed Approach to Hiding Confguration Latency in Chameleon Processors. In: FPL. Volume 1896., Villach, Austria, Springer-Verlag Lecture Notes in Computer Science (LNCS) (2000) 29–38

- 11. Mei, B., Vernalde, S., De Man, H., Lauwereins, R.: Design and Optimization of Dynamically Reconfigurable Embedded Systems. In: Proceedings of Engineering of Reconfigurable Systems and Algorithms (ERSA), Las Vegas, Nevada, USA (2001) 78–84

- Moscu Panainte, E., Bertels, K., Vassiliadis, S.: Instruction Scheduling for Dynamic Hardware Configurations. In: Proceedings of Design, Automation and Test in Europe 2005 (DATE 05), Munich, Germany (2005) 100–105

# Reconfigurable Embedded Systems: An Application-Oriented Perspective on Architectures and Design Techniques

M. Glesner, H. Hinkelmann, T. Hollstein, L.S. Indrusiak, T. Murgan, A.M. Obeid, M. Petrov, T. Pionteck, and P. Zipf

Institute of Microelectronic Systems, Darmstadt University of Technology, D-64283 Karlstr. 15, Darmstadt, Germany glesner@mes.tu-darmstadt.de

**Abstract.** Reconfiguration emerged as a key concept to cope with constraints regarding performance, power consumption, design time and costs posed by the growing diversity of application domains. This work gives an overview of several relevant reconfigurable architectures and design techniques developed by the authors in different projects and emphasizes the effective role of reconfigurability in embedded system design.

### 1 Introduction

Embedded systems have specific requirements and perform tasks, which must run generally with power consumption and real-time operation constraints while keeping design and maintenance costs low. By utilizing run-time adaptable hardware, reconfigurable architectures offer a trade-off between the performance of ASICs and the flexibility of less power efficient general purpose processor.

Reconfigurability offers several key advantages. Functionality on demand: hardware functionality can be changed or optimized after system deployment. Acceleration on demand: certain applications can be accelerated by customizing data-paths and operators on a massive parallel scale. Shorter time-to-market: hardware configuration and software can be developed in parallel, which implies great flexibility to late design changes and bug fixes. Extended product life-cycles: as flexibility is preserved, manufactured devices can be adapted to standard or customer specifications not considered at design time. Low design & maintenance costs: functionality adaptation (specialization, upgrade, acceleration), reduced development time and extended life-cycle imply low design and maintenance costs, the most salient feature of reconfigurable architectures.

Based on a set of industry and academia relevant applications, this paper gives an overview of reconfigurable architectures for embedded systems and the design thereof. The paper tries by no means to be exhaustive as the main focus lies on architectures and methodologies developed by the authors in different projects. The paper is organized as follows: section 2 presents three case studies applying reconfigurable architectures for multi-functional support, dynamic power-performance management, and DSP-specific architectural optimization. Section 3 discusses system integration issues for reconfigurable systems at different abstraction levels. Section 4 describes methodologies for reconfigurable systems design and validation. The paper concludes with some final remarks.

### 2 Applications and Architectures

**Functional Optimization and Multi-functional Support.** Reconfigurable platforms allow embedded devices to be upgraded, optimized or modified after deployment to final protocol standards or to architectural and algorithmic solutions which were not even considered at design time. In order to reduce design costs and risks, designers aiming for an early presence on the market focus more and more on flexible architectural solutions. A typical application scenario where the standardization process spans a long period of time are optical transport networks (OTN). In order to reduce re-spin costs, we proposed a multiple-core adaptive extension for overhead processing to a multi-rate forward error correction code device developed by Lucent Technologies [1].

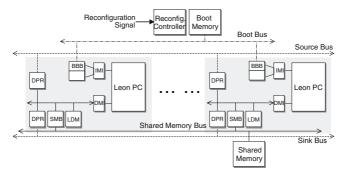

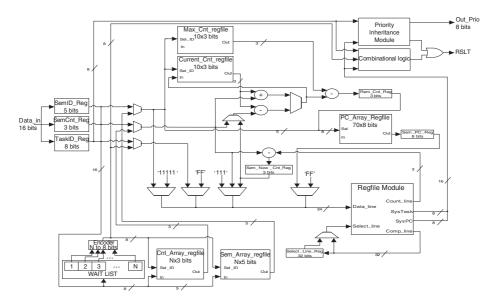

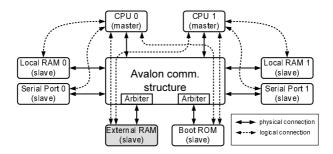

As represented in Fig. 1, a node processing block is built around the isolated Integer Unit (IU) of the Leon2 processor. Incoming data blocks are sent to each node through the Source Bus and a Dual-Port RAM. Similarly, after the data is processed, the nodes send the resulting data packets through the Sink Bus. A run-time functional modification is realized by using the double program memory of each Boot Bus Bridge (BBB), as processor cores can switch between the two program memories. A system update implies that modified code is loaded into the boot memory and afterwards into the BBB. Multi-standard support can be implemented in a similar fashion. Additionally, the nodes can also communicate via a Shared Memory and the isolated IUs can be extended with dedicated or reconfigurable logic for performance improvement [1].

**Dynamic Power-Performance Management.** Architecture optimization for low-power can be either static, assuming a worst case scenario at design-time, or dynamic, when the architecture needs to be extended to support run-time reconfigurability. In our research, we have chosen the Viterbi decoder as a case study, as it accounts for a significant percentage of the power consumption in digital receivers. The main contributor is the survivor management block, whose power consumption increases linearly with the length, which is a parameter of the design and directly affects the performance. By dynamically adjusting this length according to the run-time variations in the channel quality, significant power savings can be achieved.

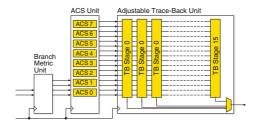

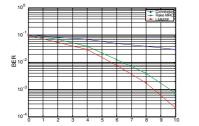

Within the scope of our research we have developed an architecture for the traceback unit that allows its length to be adjusted dynamically [2], thus saving power by

Fig. 1. Multiple-Core Architecture for Overhead Processing

Fig. 2. Viterbi Decoder with Adjustable Trace-Back

keeping only the active part on, together with an algorithm for determining the optimal trace-back window length which ensures a target bit error rate of the decoded output. In order to determine the BER experimentally as a function of different factors, a highly parameterizable simulation chain has been created using SystemC. It allows a sweep analysis of the *BER* as a function of two variables: trace-back window length and the *SNR* of the channel. The architecture consisting out of Branch Metric Unit (BMU), Add-Compare-Select (ACS), and Trace-Back (TB) Unit is depicted in Fig. 2, where the trace-back has been pipelined into 16 stages [3]. When lower performance is required, the unused stages are disabled, thus saving power. Determining the optimum length for a given SNR and puncturing pattern is done externally by an embedded processor. We applied the principle of dynamic power reduction to a state-parallel Viterbi decoder for the IEEE 802.11a standard implemented in a 0.13um CMOS library and demonstrated power savings of up to 62% [3].

**Architectural Optimization for Specific DSP Applications.** One of the main problems with reconfigurable solutions is the overhead area and power consumed by reconfiguration resources. Reconfiguring vectors rather than bits and thus achieving notable area savings, Coarse-Grained Reconfigurable Architectures (*CGRA*) have attracted lots of attention in both research and industry communities. In order to achieve further savings in reconfiguration resources a pragmatic solution is to focus on the DSP algorithms to be realized by the CGRA. By studying the data-flow graphs of these algorithms, common features can be extracted and specific design decisions can be taken, tailoring the CGRA to the DSP applications of interest.

In the context of our research, we have studied several DSP algorithms including filtering, FFT, DCT, and Viterbi decoding. We started out by studying their data flow graphs, and their reported VLSI implementations. Thereafter, parameterizable VHDL models were developed and tested [4, 5]. This paved the way for realizing a CGRA that can efficiently solve these DSP algorithms.

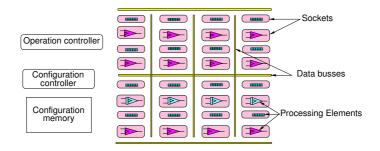

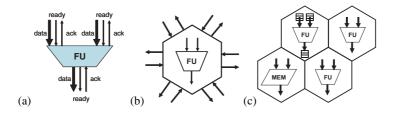

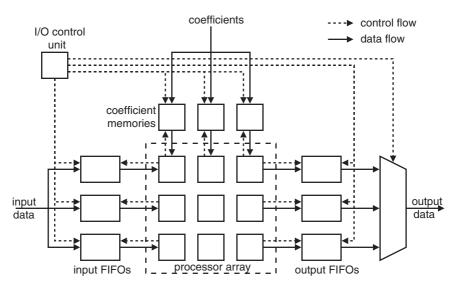

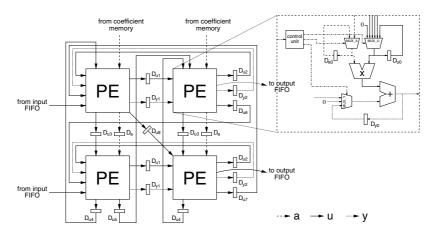

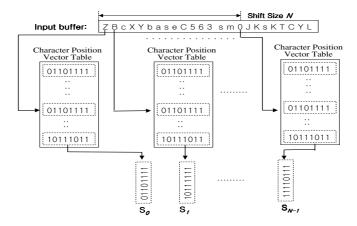

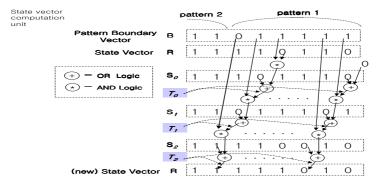

Our approach (simplified in Fig. 3) is to use a Hybrid CGRA of processing elements (*PEs*) of different types. Spreading the functionality on different types of PEs helps in realizing a more area-efficient reconfigurable array, yet maintaining the required functionality. Two types of logic and arithmetic PEs along with memory manipulations PE are used. A configuration and operation controller orchestrates the operation and reconfigurations of the Hybrid CGRA Block.

The issue of dynamic reconfiguration is an important one to address not only because of the advantages and opportunities that can be visited by having such a capability,

Fig. 3. Hybrid Reconfigurable DSP Architecture

but moreover to facilitate the implementation of some techniques that require dynamic reconfiguration of the data path on the fly, take the Radix 2 Single Delay Feedback architecture (R2SDF) as an example [6]. To address this problem we propose to solve the dynamic reconfiguration problem in two parts: locally and globally. Locally: all PEs as well as interconnection resources are placed in sockets having a set of configuration bits stored in local registers. Globally: the operation controller selects the configuration of the PE from the set stored in the socket and the configuration controller updates the local configuration bits in the sockets.

### 3 System Integration

**Processor Integration of Reconfigurable Architectures.** In a typical embedded systems scenario, a regular processor takes control over the system and the application, while reconfigurable hardware is applied to accelerate certain computation-intensive tasks. In such systems the question is how to couple processors and reconfigurable architectures. A common classification is to distinguish between the direct integration of a reconfigurable architecture into the data-path of a processor (i.e. as a reconfigurable functional unit = RFU), its connection as a coprocessor or its attachment as a peripheral device via an I/O bus. A description of advantages and disadvantages of each class can be found in [7], as well as various references to architecture examples. RFUs represent the tightest form of coupling and therefore reduce communication costs with the processor to a minimum, making it possible to map efficiently even smallest tasks to the RFU. However, as pointed out in [8], several drawbacks and severe integration problems have to be considered, e.g. the lack of a separate memory interface for the RFU or pipeline conflicts that have to be solved at run-time. Contrary to this, coprocessors and peripherals are easier to integrate and require less processor control, but communication costs are higher. Thus, they are better suited to execute larger tasks that can run independently from the processor.

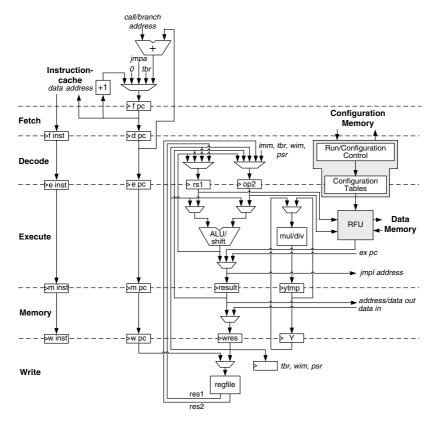

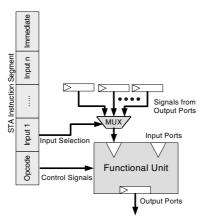

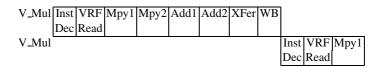

In [7] and [8] we propose a solution for integrating an RFU into a complex RISC processor that combines advantages of all three integration possibilities and is shortly presented in the following. The respective reconfigurable architecture has been developed during our research on reconfigurable computing systems for the MAC layer of

Fig. 4. Pipeline of the LEON2 processor with integrated RFU

WLANs and is capable to perform error detection/correction and cryptographic operations. It has been integrated as an RFU into the 5-stage instruction pipeline of the LEON2 processor, which had to be modified appropriately as shown in Fig. 4. To avoid pipeline conflicts, additional hold signals have been inserted that enable the RFU and the processor to coordinate and to stall each other on demand [8]. The instruction set of the LEON2 has been extended by three RFU specific instructions: two for initiating RFU operations (lasting one or multiple cycles) and one for reconfiguring the RFU. Inside the RFU, these instructions are decoded and processed by a novel configuration and run control unit [7]. It controls reconfiguration and data processing operations independently from the processor, thus significantly reducing the related overhead. With the help of several interacting configuration tables and a dedicated configuration memory, it is possible to dynamically reconfigure the device every clock cycle. The RFU has also been extended with a memory interface and dedicated control circuitry, allowing it to efficiently process large data blocks while the processor can work in parallel on different tasks. Simulation and synthesis results prove our concept and show a significant performance gain [8].

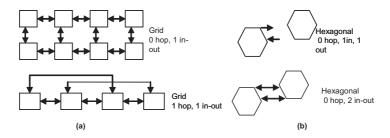

NoC-Enabled System-Level Reconfiguration. System-on-Chip (SoC) integration of multiple components, which are reconfigurable at IP block level (embedded FPGA or processor cores), poses new challenges concerning system reconfigurability. In this context, several scenarios can be assumed: reconfigurable SoC platforms used for customizing different product derivatives based on the same underlying SoC hardware (static configuration, firmware updates reconfiguration); flexible hardware platforms performing several tasks in parallel with dynamic resource allocation (dynamic reconfiguration, time-dependent task assignments). System-level reconfiguration can be understood as the reconfiguration of the implemented functionality of one or multiple SoC IP cores (FPGAs, processors). In many cases such a reconfiguration will end up in a modified communication profile within the overall SoC on-chip communication. In order to be able to provide the required communication flexibility, the on-chip interconnection architecture must provide a dynamic backbone, which can provide the required communication modes and sufficient bandwidth. Networks-on-Chip (NoCs) provide a new interconnection paradigm: abstraction of the real communication architecture as NoCattached components can communicate by using virtual addresses. Several proposals for SoC architectures have been presented:[9] (Philips), NOSTRUM [10], SOCBUS, PROTEO, SPIN, HiNoC [11], to cite only a few.

Increased difficulties for clock distribution in large SoCs, imply the requirement of asynchronous communication at the top level, which leads to the so-called Globally Asynchronous and Locally Synchronous (GALS) design style. The proposed *HiNoC*[12] system for on-chip communication supports those designs and offers support for dynamic system-level reconfiguration. Moreover, it provides both packet-based (best-effort) and stream-based (with guaranteed Quality-of-Service) communication services.

In contrast to other approaches, *HiNoC* provides a top-level mesh-based topology and on the second level within synchronous domains a fast FAT-tree based network (two-level topology). An essential property, which makes *HiNoC* unique is the inherent support of heterogenous topologies. By combining static and dynamic routing, dynamically changing architectures can be realized.

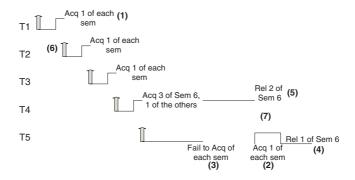

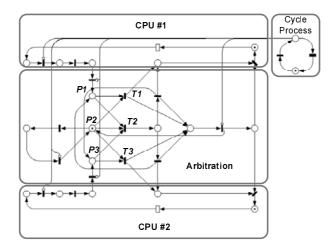

Figure 5 illustrates two operational scenarios in one NoC-based system. In the first scenario, processes *P*1 to *P*5 are running. In contrast to that, *P*4 and *P*5 are not running in the second scenario. This could be because the task requiring those two processes has finished. Since the associated hardware resources are unused, the network can be partly shut down if the remaining links can fulfill the communication requirements of the system in the new configuration. The right part of Fig. 5 depicts the architectural changes to the system. The *HiNoC* Communication Architecture provides a time-division multiplex access scheme which is combined with a wormhole routing method (possibility

Fig. 5. HiNoC: Operational Scenarios

of folding packets and streams). Connections with guaranteed bandwidth (QoS) are set up by a connection request packet.

The main problem of data transfers between truly independent clock domains is the possibility of metastability in the receiving flip-flops. To avoid metastability in such asynchronous communication fast and robust synchronization techniques must be employed. In a conventional synchronous design, each bit of transferred data is assumed to become stable long enough before the next clock edge. Data transfers can thus be implemented by directly connecting the output of the sending module to the input registers of the receiving module. After the incoming data became stable, it is written into the registers with the rising edge of the clock signal. In a globally asynchronous system, there is no dependency of the clocking of an individual module on another. Because of this missing dependency, no assumption can be made on the time difference between the transition of an incoming data or control signal and the next local clock edge. If both transitions appear at the receiving flip-flop within a time-frame small enough (in terms of its setup and hold times), then the flip-flop can become metastable.

Several approaches for synchronization have been proposed which can be applied to NoC switch communication, including FIFO buffers [13], self-synchronization [14], or adaptations of clock stretching [15]. Our own experiments with NoC switch designs indicate that it is possible to obtain save and efficient implementations [16] for the asynchronous switch communication.

### 4 Methodologies for System Design and Validation

Reconfigurable systems inherit most of the design complexity of regular hardware/software systems. Thus, the design methodologies for reconfigurable systems are also based on model refinement across several abstraction layers. The added complexity of designing and validating reconfiguration mechanisms is currently addressed in the lower abstraction layers. For FPGA based systems, a common approach is the Modular Design Flow, which advocates that different configurations should be designed separately at RTL after an initial floor-plan budgeting [17]. While such low-level methods for reconfiguration are necessary, we advocate here a system-level view in order to actually validate the benefits of reconfigurability within an application scenario. Such scenarios are usually modeled as complex testbenches that are unpractical in RTL, and the accurate modeling of their dynamic nature is particularly critical in the case of runtime reconfiguration. Thus, designers must first design the system and its testbench in a high abstraction level, in order to allow for design space exploration, and in a second step the system must be designed in lower levels - logic or RTL - so that its implementation-specific features can be defined. In order to validate the low-level implementation model, its co-simulation with the high-level testbench (or at least part of it) should be possible.

The approach presented here to cope with such demands is strongly based on the actor-oriented design methodology presented by Lee et al [18]. We explore the concept of actors to model both the reconfigurable systems and the application scenarios where they are inserted, allowing for a well defined strategy for system modularization. Once the actors are well defined, it is possible to refine each one of them individually towards

implementation models in logical or RTL level. It is also possible to devise mechanisms to allow the simulation of the implementation models with the remaining actors by encapsulating them (together with their respective simulators, when possible) as actors.

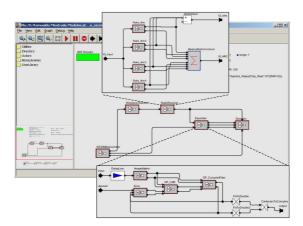

As a case study, we applied such approach on the design of a self-reconfigurable receiver for WCDMA down-link UMTS standard. This receiver can self-adapt to the conditions of the transmission channel due to multi-path [19], combining the conventional Rake receiver with maximal ratio combining (MRC) and a linear minimum mean squared error (LMMSE) equalizer. We first explored the actor-oriented modeling capabilities of Ptolemy II [20] by creating models of both the receiver and its usage scenario including user mobility patterns and transmission channel conditions. The accurate description of the application scenario increases significantly the complexity of the model, therefore it is implemented in a high level of abstraction using floating point arithmetic. Figure 6 shows PtolemyII GUI displaying the top-level model of the communication system. The composite actors *RakeReceiver* and *Equalizer* are also shown in a lower hierarchical level as those are the ones to be implemented in hardware. By simulating the system in PtolemyII, designers can navigate over the design space by parameterizing the receiver and analyzing the bit error rate (BER) under different channel models. The implemented case study used the channel described in [20].

After the analysis and profiling of the system model, the hardware implementation of the receiver was started: Rake receiver, MRC and the MMSE linear equalizer. We used JHDL [21] to create lower abstraction models of the subsystems that should be implemented in hardware. JHDL is a HDL based in Java and was chosen for the simplicity of integration with PtolemyII, as shown in [22], but there is no restriction on this point and the methodology would be the same if other HDL such as SystemC or VHDL were used. While some early conceptual work is shown in [18], no automated path from PtolemyII models to JHDL descriptions are available, thus the implementation is based on iterative refinement. In order to validate the refinement steps, every module written in JHDL should be encapsulated within an actor, integrated into Ptole-

Fig. 6. Top-level system view in PtolemyII

**Fig. 7.** a) BER versus SNR for receiver in a vehicular channel with 120Km/h, spreading factor 64, and 15 users; b) BER versus number of users for a receiver in a vehicular channel with 60Km/h, spreading factor 64 and SNR 10dB

myII and co-simulated together with the whole model, allowing designers to evaluate the performance of the implemented subsystem under the constraints and conditions modeled within the testbench. The results of such simulations are shown in Fig. 7. A single correlator receiver is also shown just to give an idea about the performance of the other receivers. The JHDL toolset provides facilities to export EDIF netlist which allowed for mapping the implemented system in FPGA. The whole receiver was mapped in a Xilinx XCV800 FPGA using 4793 out of 9408 slices and operating at 15.672 MHz, which is more than enough for the WCDMA standard. Current research aims to address the verification of the final implementation in FPGA with the testbench implemented within PtolemyII. Such co-simulation platform will reuse the reconfigurable hardware encapsulation approach presented in [23].

### 5 Final Remarks

Reconfigurability plays a key role in the design of embedded systems as it helps to overcome the traditional trade-off between the performance of ASICs and the flexibility of general purpose processors. Based on a selected set of relevant applications, this paper presented various functional and architectural optimization strategies, system integration concepts and design-and-validation methodologies, proving thus the effectiveness of employing reconfigurable platforms for the development of embedded systems in terms of functionality, performance, time-to-market, life-cycle improvement, and design and maintenance costs.

#### References

- 1. Murgan, T., Petrov, M., Majer, M., Zipf, P., Glesner, M., Heinkel, U., Pleickhardt, J., Bleisteiner, B.: Adaptive architectures for an OTN processor: Reducing design costs through reconfigurability and multiprocessing. In: ACM Computing Frontiers Conf. (2004) 408–414

- Petrov, M., Obeid, A.M., Murgan, T., Zipf, P., Brakensiek, J., Oelkrug, B., Glesner, M.: An adaptive trace-back solution for state-parallel Viterbi decoders. In: IFIP Intl. Conf. VLSI, Darmstadt, Germany (2003) 167–172

- 3. Petrov, M., Murgan, T., Obeid, A.M., Chiţu, C., Zipf, P., Brakensiek, J., Glesner, M.: Dynamic power optimization of the trace-back process for the Viterbi algorithm. In: IEEE Intl. Symp. Circuits and Syst., Vancouver, Canada (2004) 721–724

- 4. Obeid, A.M., García, A., Glesner, M.: A constraint length and throughput parameterizable architecture for Viterbi decoders. In: IEEE Int. Conf. Microelectronics. (2004)

- Obeid, A.M., García, A., Petrov, M., Glesner, M.: A multi-path high speed Viterbi decoder. In: IEEE Int. Conf. Electronics, Circuits and Syst. (2003)

- 6. He, S., Torkelson, M.: Design and implementation of a 1024-point pipeline FFT processor. In: IEEE Custom Integrated Circuits Conf. (1998) 131 –134

- 7. Pionteck, T., Stiefmeier, T., Staake, T., Kabulepa, L., Glesner, M.: Integration dynamisch rekonfigurierbarer funktionseinheiten in prozessoren. In: Int. Conf. Architecture of Computing Systems. (2004)

- Hinkelmann, H., Pionteck, T., Kleine, O., Glesner, M.: Prozessorintegration und speicheranbindung dynamisch rekonfigurierbarer funktionseinheiten. In: Int. Conf. Architecture of Computing Systems. (2004)

- 9. Rijpkema, E., Goossens, K., Rădulescu, A., Dielissen, J., van Meerbergen, J., Wielage, P., Wateralnder, E.: Trade-offs in the design of a router with both guaranteed and best-effort services for networks on chip. IEE Proc. Comput. Digital Techniques **150** (2003) 294–302

- Kumar, S., Jantsch, A., Soininen, J.P., Forsell, M., Millberg, M., Öberg, J., Tiensyrjä, K., Hemani, A.: A network on chip architecture and design methodology. In: Proc. VLSI Ann. Symp. (2002) 105–112

- 11. Hollstein, T., Ludewig, R., Mager, C., Zipf, P., Glesner, M.: A hierarchical generic approach for on-chip communication, testing and debugging of SoCs. In: Proc. of VLSI-SoC. (2003)

- 12. Hollstein, T., Zimmer, H., Hohenstern, S., Glesner, M.: HiNoC: A flexible multi-mode transmission network-on-chip platform. In: Proc. Baltic Electronics Conf. (2004)

- 13. Chelcea, T., Nowick, S.M.: Robust interfaces for mixed-timing systems with application to latency-insensitive protocols. In: Proc. Design Automation Conf., Las Vegas, CA (2001)

- 14. Mu, F., Svensson, C.: A 750Mb/s 0.6μm CMOS two-phase input port using self-tested self-synchronization. In: IEEE Int. Conf. Solid-State Circuits. (1999)

- 15. Mead, C., Conway, L.: Introduction to VLSI Systems. Addison-Wesley (1980)

- Zipf, P., Hinkelmann, H., Ashraf, A., Glesner, M.: A switch architecture and signal synchronization for GALS system-on-chips. In: Proc. Symp. Integrated Circuits and Syst. Design, Porto de Galinhas, Pernambuco, Brazil (2004) 210–215

- 17. Xilinx Inc. http://toolbox.xilinx.com/docsan/xilinx6/books/docs/dev/dev.pdf: Development System Reference Guide. (2003)

- 18. Lee, E.A.., Neuendorffer, S., Wirthlin, M.J.: Actor-oriented design of embedded hardware and software systems. Journal of Circuits, Systems, and Computers 12 (2003) 231–260

- 19. Hooli, K.: Equalization in WCDMA Terminals. PhD thesis, Oulu University Press (2003)

- 20. Harada, H., Prasad, R.: Simulation and Software Radio for Mobile Communication. Artech House Publishers (2002)

- 21. Bellows, P., Hutchings, B.L.: JHDL an HDL for reconfigurable systems. In: Proc. FCCM98, Napa Valley, CA (1998)

- 22. Wirthlin, M.: Integration of JHDL and PtolemyII. Available at http://www.ee.byu.edu/faculty/wirthlin/projects/ptjhdl.htm (2005)

- Indrusiak, L.S., Lubitz, F., Reis, R., Glesner, M.: Ubiquitous access to reconfigurable hardware: Application scenarios and implementation issues. In: Proc. DATE. (2003) 940–945

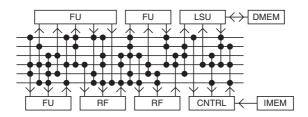

# **Reconfigurable Multiple Operation Array**

Humberto Calderon and Stamatis Vassiliadis

Computer Engineering Laboratory,

Electrical Engineering Dept., EEMCS, TU Delft, The Netherlands

{H.Calderon, S.Vassiliadis}@ewi.tudelft.nl

http://ce.et.tudelft.nl

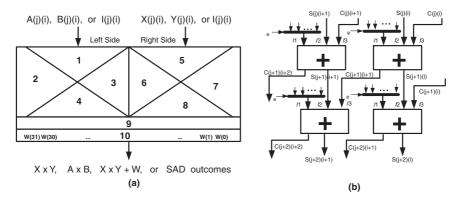

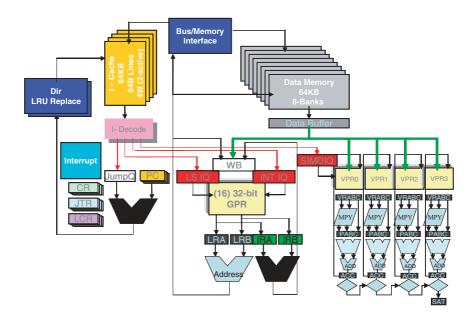

**Abstract.** In this paper, we investigate the collapsing of eight multi-operand addition related operations into a single and common (3:2) counter array. We consider for this unit multiplication in integer and fractional representations, the Sum of Absolute Differences (SAD) in unsigned, signed magnitude and two's complement notation. Furthermore, the unit also incorporates a Multiply-Accumulation unit (MAC) for two's complement notation. The proposed multiple operation unit was constructed around 10 element arrays that can be reduced using well known counter techniques, which are feed with the necessary data to perform the proposed eight operations. It is estimated that 6/8 of the basic (3:2) counter array is shared by the operations. The obtained results of the presented unit indicates that is capable of processing a 4x4 SAD macro-block in 36.35 ns and takes 30.43 ns to process the rest of the operations using a VIRTEX II PRO xc2vp100-7ff1696 FPGA device.

### 1 Introduction: The Need for Reconfigurability

The need of multimedia Instruction Set Architectures (ISA) extensions with high performance processing and flexibility characteristics are potentially met with the use of reconfigurable technologies[1]. The new emerging capabilities in Reconfigurable Computing (RC) are letting us to dynamically reconfigure a portion of a FPGA. Reconfigurable fabrics can be used to support a common and basic logic blocks intended to be used in several operand addition related operations. The common blocks can be configured in advance; therefore, the hardware differences needed for performing a particular operation will be reconfigured partially based on the hardware differences between the common basic array and the new needed functionalities, instead of programming totally the new entire desired operation [2]. This work presents the collapsing of eight multi-operand addition related operations into the common hardware suitable to be implemented into a VLSI as a run time configurable unit and also over a reconfigurable technology as a reconfigurable run time unit. The multiple operation array has the following embedded units and features:

- A 16 x 16 bit multiplier for integer and fractional representations with universal notations <sup>1</sup>.

- A 4 x 4 picture elements concurrent SAD macro-block in universal notation.

<sup>&</sup>lt;sup>1</sup> Universal notation, in the context of this article, assumes operands and results to be in unsigned, sign magnitude and two's complement notations.

T.D. Hämäläinen et al. (Eds.): SAMOS 2005, LNCS 3553, pp. 22-31, 2005.

- The Multiply-Accumulation Unit (MAC) for two's complement notation.

- A performance of 35.6 ns for 4x4 SAD macro-block and 30.43 ns for the rest of 7 operations.

The paper is organized as follows. Section 2 outlines the Reconfigurable Multiple Operation Array organization. Section 3 presents the experimental results of the mapped unit, as well as other comparison units in terms of area used and time delay. Finally, the article is concluded in section 4.

### 2 Reconfigurable Multiple Operation Array

This section begins presenting a background and relevant work; consequently, a general array description of the Reconfigurable Multiple Operation Array is described. Finally, a complete description of the equations set for the construction and reproduction of the proposed unit are shown.

### 2.1 Background and Related Work

Motion estimation techniques divide an image frame for its processing in macro-blocks of n \* n picture elements (pels). The processing establishes if there is a difference between two image blocks using the Sum of Absolute Differences (SAD) operation, establishing the pels differences between two chosen frames. Equation (1) states the metric to evaluate the searched block.

$$\sum_{i=1}^{16} \sum_{i=1}^{16} |IN1(x+i, y+j) - IN2((x+r)+i, (y+s)+j)|$$

(1)

where, the duple (x,y) represents the position of the current block, and the pair (r,s) denotes the displacement of IN2, relative to reference block IN1. Different investigations including a previous author's work have been proposed to speed up the critical SAD kernel [3],[4],[5]. The processing requires that SAD input terms received by the multiple operation array have to be ordered previously, in order to compute correctly the operation; therefore, the absolute operation |IN1 - IN2| can be substituted, with IN1 - IN2 or IN2 - IN1 depending whether IN1 or IN2 is the smallest and thus obtaining a positive result. As is suggested in [5] we can make this operation inverting one of the operands and computing the carry out of the addition of both operands as stated by the following equations:

$$\overline{IN1} + IN2 \ge 2^i - 1 \tag{2}$$

therefore

$$IN2 > IN1$$

(3)

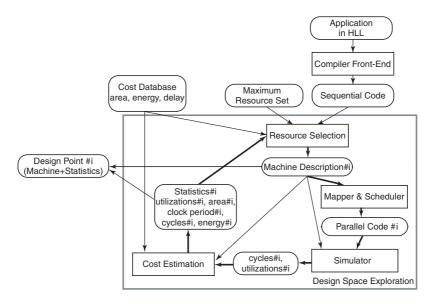

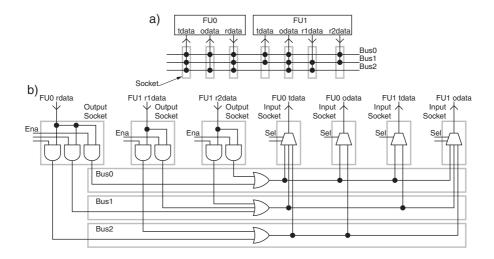

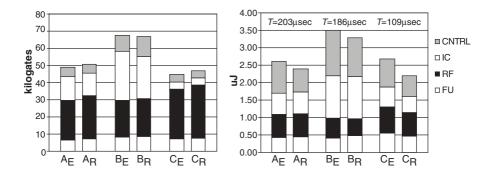

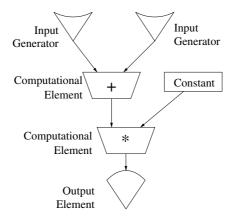

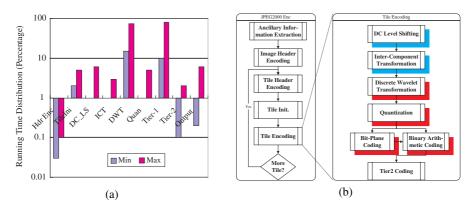

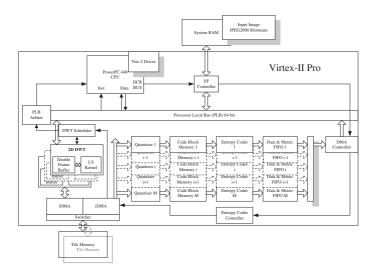

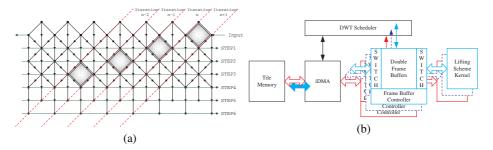

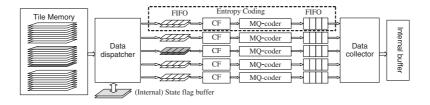

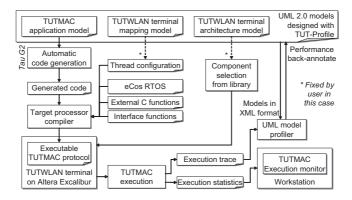

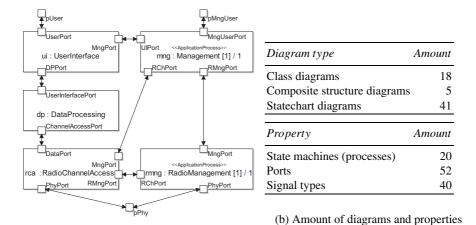

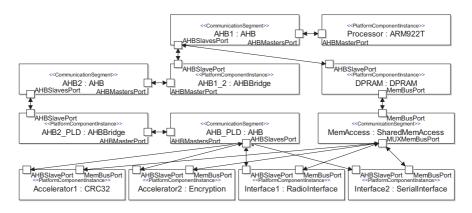

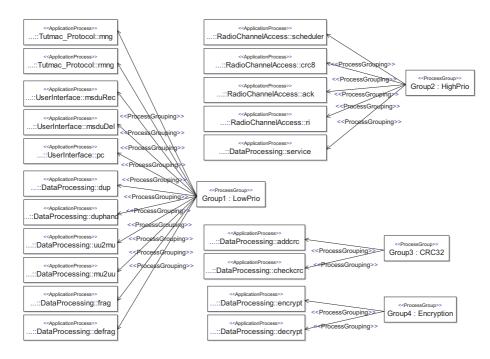

means checking whether the addition of the bit inverted *IN1* and the operand *IN2* produces a carry out. The outcome determines which one is the smallest, depending on the existence or not of the carry output. Consequently, a simple logic can be used to correct the terms and feed the array. Regarding universal units capable to work with universal notations, the reader is referred to view the predecessor unit in [6] and a recent reintroduction in [7]. An extra row of (3:2)counter for MAC operation is used